Parity generator proposed bits example Implementation qca parity Proposed parity generator circuit (example is for 16 bits)

Proposed parity generator circuit (Example is for 16 bits) | Download

Parity generator bit using odd circuit mux create implement solved inputs transcribed text show problem been has Solved create a 3-bit odd parity generator circuit using an Step by step method to design a combinational circuit – vlsifacts

Solved: derive the circuits for a 3-bit parity generator and 4

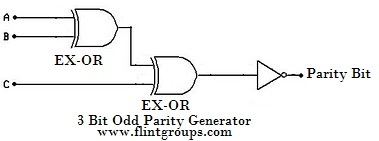

The four-bit parity generator and checker circuitVhdl tutorial – 12: designing an 8-bit parity generator and checker Parity derive circuitsParity odd generator bit circuit.

Parity bit- even & odd parity checker & circuit(generator)C++ programming for beginners: parity generator 3-bit odd parity generator circuitParity generator odd bit circuit example logic circuits common figure.

7.5: design of common logic circuits

Parity generator and parity checker3 bit parity checker Parity checker technobyteVhdl tutorial – 12: designing an 8-bit parity generator and checker.

Parity vhdl checkerCircuit parity generator even combinational step method Parity checker bit circuit circuitlab descriptionParity generator bit even circuit odd three inverter contain does.

Parity bits odd bit even generators do table example binary number vs data logic numbers mathematics digital checkers many has

Qca implementation of 4-bit even parity generator circuit using theParity generator bit checker circuit diagram Parity checker vhdl circuits designingParity odd bit checker even generator circuit.

.

C++ Programming For Beginners: Parity Generator

3 bit parity Checker - CircuitLab

The four-bit parity generator and checker circuit | Download Scientific

QCA implementation of 4-bit even parity generator circuit using the

Step by Step Method to Design a Combinational Circuit – VLSIFacts

Parity Bit- Even & Odd Parity Checker & Circuit(Generator) - YouTube

Proposed parity generator circuit (Example is for 16 bits) | Download

7.5: Design of Common Logic Circuits | GlobalSpec

VHDL Tutorial – 12: Designing an 8-bit parity generator and checker